Displaying Document(s) For : All Categories

Solution Brief

Last Updated: May 05, 2026

Powered by Intel® Xeon® 6 SoCs, the FTA 5190, handles larger key size and complex math needed for post-quantum cryptography (PQC).

Published By:

Tags:

Intel® Xeon® Scalable ProcessorsCryptographyCybersecurity

Solution Brief

Last Updated: May 05, 2026

Company demonstrates computer vision-based retail product recommendation application powered by Intel’s Edge AI portfolio

Published By:

Tags:

Artificial IntelligenceRetailIntel® Core™ Processor

Partner Brief

Last Updated: May 05, 2026

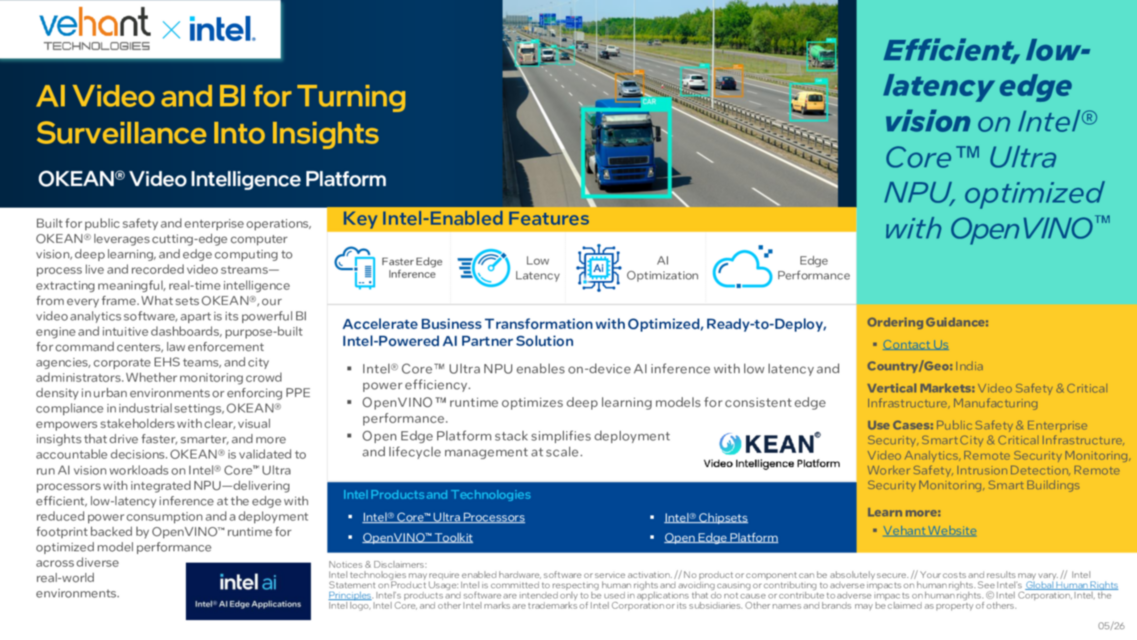

Built for public safety and enterprise operations, OKEAN® leverages cutting-edge computer vision, deep learning, and edge computing to process live and recorded video streams—extracting meaningful, real-time intelligence from every frame. What sets OKEAN®, our video analytics software, apart is its powerful BI engine and intuitive dashboards, purpose-built for command centers, law enforcement agencies, corporate EHS teams, and city administrators.

Published By:

Tags:

Machine LearningArtificial IntelligenceMedia AnalyticsVideo Analytics

Partner Brief

Last Updated: May 05, 2026

Falcons Defender is an edge-based AI solution developed by Toronto-based Falcons.AI, embodying a Canadian approach to privacy first innovation and responsible AI. Designed to help organizations proactively detect and block NSFW imagery, it supports regulatory compliance while strengthening digital safety. As regulations tighten, enterprises need immediate visibility into image data flowing across their infrastructure—without sacrificing privacy or performance.

Published By:

Tags:

Artificial IntelligenceVideo AnalyticsIntel® Core™ Processor

Solution Brief

Last Updated: May 05, 2026

HP and Intel join forces to deliver secure, revolutionary remote management and remediation with the HP Workforce Experience Platform (WXP) and Intel vPro® technology supporting business continuity.

Published By:

Tags:

RetailCybersecurity

Partner Brief

Last Updated: May 05, 2026

EdgeExl is a school curriculum aligned AI Teacher that interacts with students in real time, powered by a state-of-the art Small Language Models running entirely on a local Intel® Core™ Ultra processor (Series 2)-based desktop PC which uses HW Virtualization – SRIOV to allow the desktop compute to be shared by up to 4 users making the solution cost effective for mass adoption for the school education use case.

Published By:

Tags:

SR-IOVVirtualizationArtificial IntelligenceIntel® Core™ Processor

Reference Architecture

Last Updated: May 05, 2026

Intel® AI Edge systems enable our partners to jumpstart development through system foundations verified by Intel. Explore optimized edge AI systems with Intel® Core Ultra Processors Series 3.

Published By:

Tags:

Machine LearningArtificial IntelligenceIntel® Core™ Processor

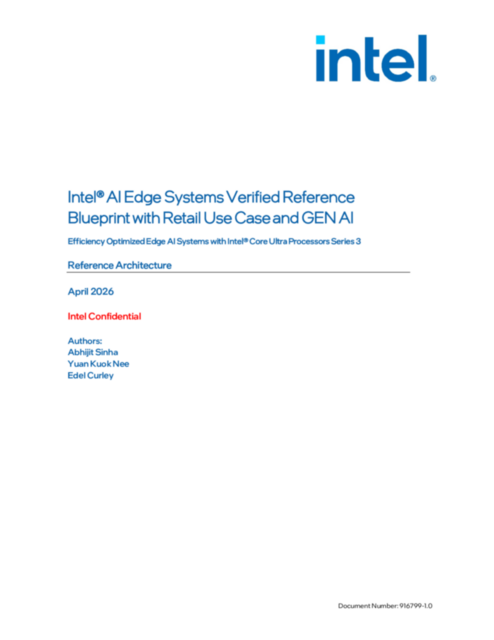

Partner Brief

Last Updated: April 22, 2026

WildFaces' WildAI delivers advanced computer vision for object detection and tracking when cameras are in motion, overcoming a key limitation of traditional fixed-sensor video analytics. The solution accurately tracks people and vehicles from PTZ cameras, drones, and mobile robots, even in dense, dynamic environments.

Published By:

Tags:

Artificial IntelligenceVideo Analytics

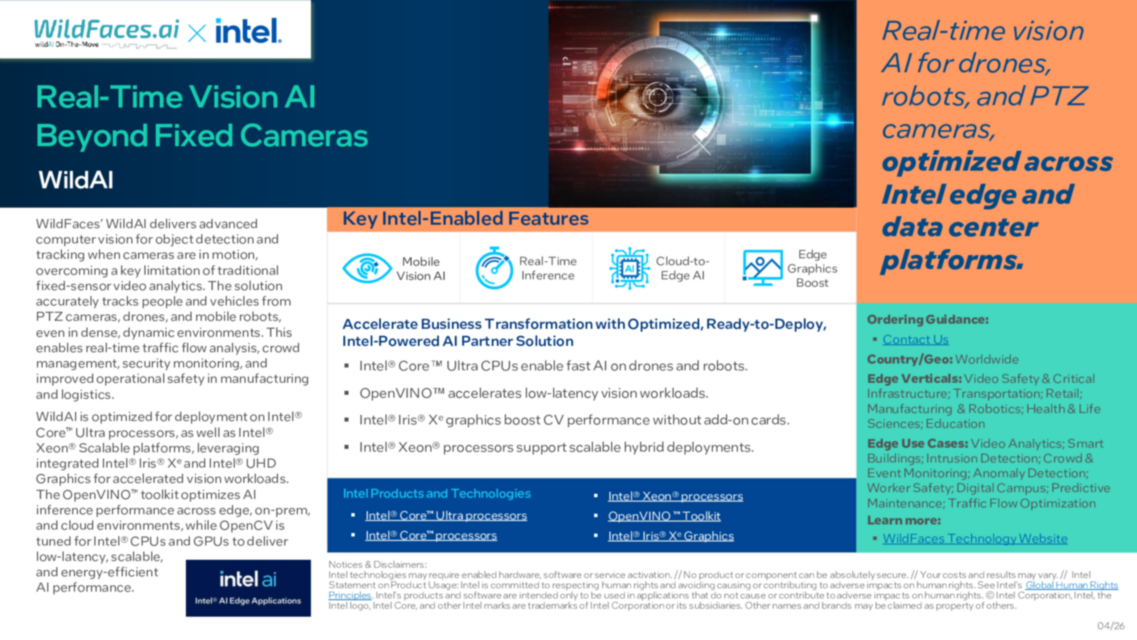

Partner Brief

Last Updated: April 21, 2026

Cognome's AutoChart uses a proprietary LLM ensemble trained on 30M+ patient records with built-in AI governance to move Population Health Management and Value-based Care from retrospective attribution and reporting to enterprise-wide Prospective Intelligence designed to support earlier interventions with the goal of delivering better patient outcomes.

Published By:

Tags:

Intel® Xeon® Scalable ProcessorsArtificial IntelligenceHealthcare

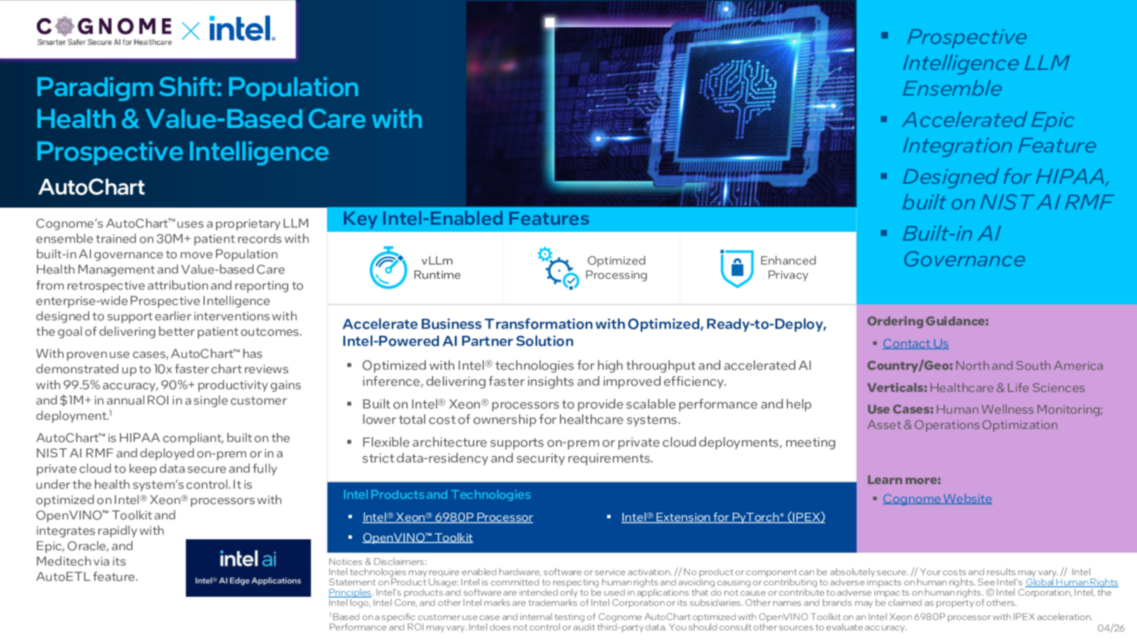

Partner Brief

Last Updated: April 21, 2026

Classera is an AI-powered learning platform designed to personalize and enrich the educational experience for every learner. It features adaptive learning paths, auto-graded assessments, real-time performance analytics, gamification, virtual classrooms, and smart content recommendations.

Published By:

Tags:

Artificial IntelligenceIntel® Core™ Processor

Partner Brief

Last Updated: April 21, 2026

ARCsafe is an AI-powered worker safety platform that turns industrial cameras into real-time safety intelligence. Built for manufacturing, it detects unsafe behaviors—hazard zone entry, missing PPE, poor posture, fatigue, and distraction—to prevent incidents before they occur.

Published By:

Tags:

Artificial IntelligenceManufacturing

Solution Brief

Last Updated: April 21, 2026

Bluefin Ocean is a digital signage platform with compute power from Intel® Processor N97 that enables dynamic content to meet the needs of retailers and a wide range of other use cases

Published By:

Tags:

Machine LearningArtificial IntelligenceRetail

Showing -

of results