## 5G NEWORK TRANSFORMATION WITH FPGAS

PAT MEAD

INTEL NETWORK & CUSTOM LOGIC GROUP

### DATA-CENTRIC INFRASTRUCTURE FOCUS

#### **MOVE FASTER**

(intel) OMNI-PATH FABRIC

#### STORE MORE

#### PROCESS EVERYTHING

#### SOFTWARE & SYSTEM-LEVEL OPTIMIZED

## CONVERGENCE OF COMPUTE AND CONNECTIVITY

REQUIRES AGILITY, SCALABILITY AND INTELLIGENCE ACROSS NETWORK, CLOUD & CLIENT

## **CLOUDIFICATION OF THE NETWORK**

#### THE NETWORK MOVES TO INTEL® ARCHITECTURE (IA)

2011

NFV DEFINED 2013

1ST NFV PROOF OF CONCEPTS 2015

20% OF COMMS SPS ADOPT NFV 2017

INTEL DPDK

MOVES TO LINUX

FOUNDATION

2019

181 100% CLOUD-NATIVE NETWORK 2020

**75%**NETWORK WILL BE VIRTUALIZED

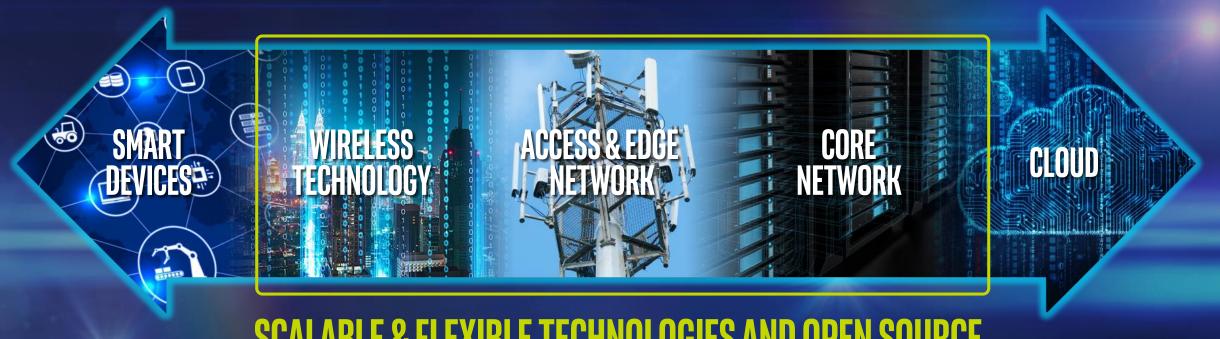

## INTEL NCLG ENABLES E2E 5G

Radio Front Haul Baseband

**FlexRAN** MEC **Back Haul**  5GCN / vEPC **NFVI** Security

### THE COMPLETE CUSTOM LOGIC PORTFOLIO

**FPGA**

STRATIX inside

SHORTEST TTM HIGHEST FLEXIBILITY NO NRE

**Jnit Price**

STRUCTURED ASIC

UP TO 60% POWER REDUCTION

COST REDUCTION

LOW NRE

**CUSTOM ASIC**

LOWEST POWER

LOWEST COST

HIGHEST PERFORMANCE

Volume

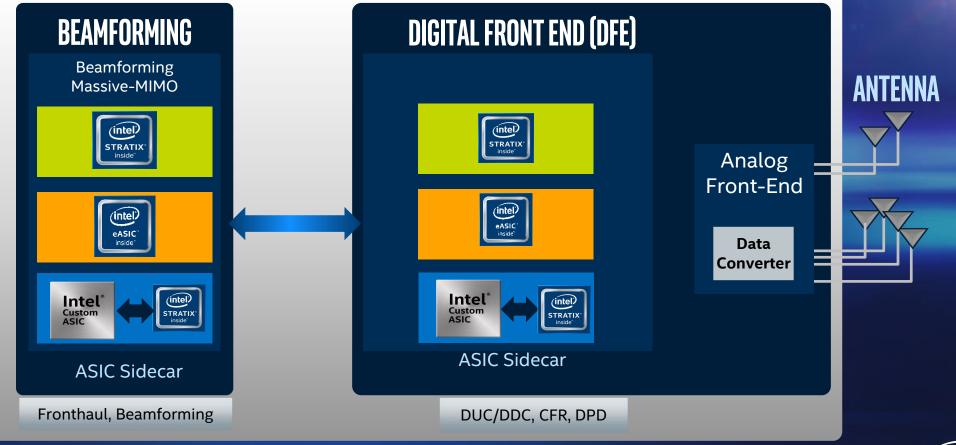

### 5G RADIO SOLUTIONS

RADIO UNIT (RU)

Time-to-Market

Cost/Power Optimization

Mass Volume Production

### **5G BASEBAND SOLUTIONS**

**BASEBAND UNIT (BBU)**

Time-to-Market

Cost/Power Optimization

Mass Volume Production

FEC + CODEC **CO-OPTIMIZED COMPONENT AND IP PLATFORM SOLUTION** SIGNAL PROCESSING **PRACH**

eMBB

uRLLC

#### FLEXIBLE FRONTHAUL SOLUTIONS

## FRONTHAUL SOLUTIONS SUPPORTED ACROSS XEON, FPGA & EASIC DEVICES

**CONNECTIVITY and FLEXIBILITY**

## TECHNICAL STANDARD REFERENCE DESIGN AND LEADERSHIP

- CPRLIP

- eCPRI IP

- RoE IP

- Compression IP

- xRAN IP

- Synchronization & 1588 IP

Fronthaul (Fiber or Copper)

### **SOLUTION COMPONENTS & ECOSYSTEM**

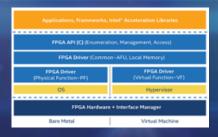

Application Software Drivers & Frameworks

**Accelerator Function**

**FPGA**

FPGA Hardware & Drivers

Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processor Platform

#### **IP/ISV Partners**

Customization, Complete Applications Production Ready

Intel NCLG

Silicon & Boards Reference designs SW Stack System Integration

### ECOSYSTEM ENABLEMENT MODEL FOR VRAN

COTS Architecture, Server Platforms (Intel® Xeon® D processor, Intel® Xeon® Scalable Processor), FPGA PAC Intel FlexRAN & vRAN

Enablement Package

L1 (PHY) 4G & 5G

٠

L2 / L3 (Stack) 4G & 5G

3<sup>rd</sup> Party SW **RRU**

OEM/TEM/SI vRAN Solution (BBU on COTS Server & SW, FPGA, RF and RRU)

**BBU SW**

Service

**Providers**

4G & 5G vRAN

Solutions

**Enterprises**

**Platforms**

Reference S/W & User Workload Optimized on IA/FPGA

Commercial Product

Intel working with eco-system to accelerate the development of vRAN solutions

### INTEL RAN SOLUTION PORTFOLIO

Intel® Xeon® Processor Intel Atom<sup>®</sup> Processor

Artificial Intelligence Intel® FPGA

Intel® eASIC ASIC

Application

Specific Products

Custom Modules Intel® PAC

#### **Enablement Software**

Open Programmable Acceleration Engine (OPAE)

Wireless Transport Production SW

Intel® FlexRAN Reference SW

#### **Standards & Industry Consortia**

Intel brings together the products, ecosystem & influence to enable next generation RAN architectures

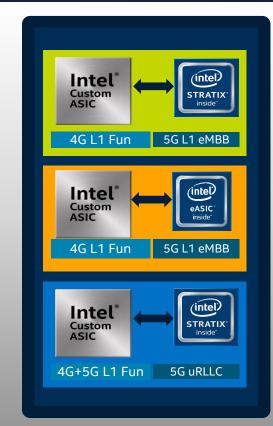

### INTEL® PAC N3000 - 4G & 5G L1 ACCELERATION

Intel® PAC N3000 Acceleration Card

- Integrated Reference Design for LTE Turbo (FEC), 5G LDPC (FEC) and XRAN/ORAN Fronthaul

- Flexibility of repurposing same hardware for different workloads

- DPDK API (BBDev) for FlexRAN PHY integration, OPAE Tools

- PCIe Gen3 x16, 2xQSFP28, Full Height, Half Length

Reference Design Program for OEM development and ecosystem partners

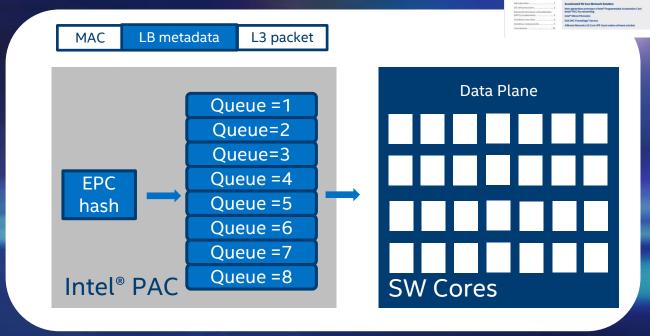

### LOAD BALANCING ACCELERATOR

#### **Overview**

- Achieved 170 Gbps on 2 x 100 GbE links using Intel® Xeon® processors and Intel® FPGA-based Programmable Acceleration Card\*

- Enabling cost-effective and scalable user plane

5G/4G core solutions for both edge and central office requirements by utilizing COTS platforms

#### Value

- Packet processing performance improvement with optimized CPU utilization

- Frees up cores for other hosted 5G services, e.g. DPI

- Reduced CapEx/OpEx

#### **Performance Gain**

- 50% core saving on user plane forwarding

- 100 GbE termination

- 20 Gbps / core

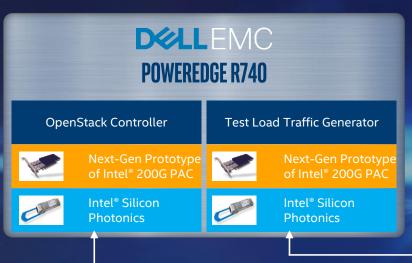

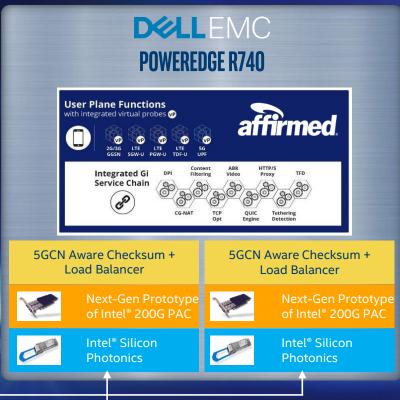

#### **200G FPGA-ACCELERATED 5GCN**

- First cloud-native containerized 5G core network with 100GbE interfaces (MWC 2019)

- Load balancing acceleration using Intel<sup>®</sup> PAC

- Affirmed 5GCN SA VNF

- User plane packet forwarding

- HW accelerated load balancing free up 12 physical core available for DPI and/or other applications

| #pCPU<br>User | Traffic Type: 50/50<br>Uplink/Downlink | Throughput per<br>Server     | Packet Rate<br>per Server | Details*                                                                                                                                                                                                                                                                                           |

|---------------|----------------------------------------|------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12            | UDP, 640 Bytes Packet                  | ~170 Gbps                    | 33 Mpps                   | <ul> <li>Intel® Skylake Platinum with 200 Gbps line rate</li> <li>Demo and corresponding core were based on 5GCN packet forwarding</li> <li>Application headroom with 44 pCPUs out of 56 pCPUs in 2 socket server with 170 Gbps throughput at application level and 193 Gbps line rate.</li> </ul> |

| 8             | UDP, 640 Bytes Packet                  | ~160 Gbps<br>(20 Gbps/pCore) | 31 Mpps                   |                                                                                                                                                                                                                                                                                                    |

# COMMUNICATIONS FPGA ECOSYSTEM

| ALTIOSTAR             | Leading solutions provider for End-to-End 4G & 5G wireless |

|-----------------------|------------------------------------------------------------|

| affirmed <sup>®</sup> | Leader in accelerated vEPC and 5GCN solutions              |

|                       | Leader in Firewall and Network Management                  |

| Krrive                | Leader in accelerated IPSec and TLS security IP            |

| <b>EENU</b> NETWORKS  | Leader in accelerated vBNG and vCPE solutions              |

| HCL                   | Global Design services and System Integration partner      |

### LEGAL DISCLAIMER

Optimization Notice: Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice. Notice Revision #20110804

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

FTC Disclaimer for Performance Claims; General Technology Disclaimer; Trademark and Copyright Notice; Cost Reduction Disclaimer; FTC Optimization Notice;

Intel, the Intel logo, [List the Intel trademarks in your document] are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© Intel Corporation